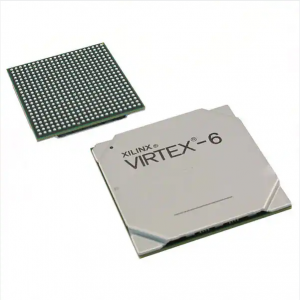

ନୂତନ ଏବଂ ମୂଳ XC6VLX240T-2FFG1759I ଇଣ୍ଟିଗ୍ରେଟେଡ୍ ସର୍କିଟ୍ |

ଉତ୍ପାଦ ଗୁଣ

| TYPE | ବର୍ଣ୍ଣନା |

| ବର୍ଗ | ଇଣ୍ଟିଗ୍ରେଟେଡ୍ ସର୍କିଟ୍ (ଆଇସି) |

| Mfr | AMD Xilinx |

| ସିରିଜ୍ | Virtex®-6 LXT | |

| ପ୍ୟାକେଜ୍ | ଟ୍ରେ |

| ଉତ୍ପାଦ ସ୍ଥିତି | ସକ୍ରିୟ | |

| LABs / CLB ର ସଂଖ୍ୟା | | 18840 |

| ଲଜିକ୍ ଉପାଦାନ / କକ୍ଷଗୁଡ଼ିକର ସଂଖ୍ୟା | | 241152 |

| ମୋଟ RAM ବିଟ୍ | | 15335424 |

| I / O ର ସଂଖ୍ୟା | 720 |

| ଭୋଲଟେଜ୍ - ଯୋଗାଣ | 0.95V ~ 1.05V |

| ମାଉଣ୍ଟିଂ ପ୍ରକାର | | ସରଫେସ୍ ମାଉଣ୍ଟ୍ | |

| ଅପରେଟିଂ ତାପମାତ୍ରା | | -40 ° C ~ 100 ° C (TJ) |

| ପ୍ୟାକେଜ୍ / କେସ୍ | 1759-BBGA, FCBGA | |

| ଯୋଗାଣକାରୀ ଉପକରଣ ପ୍ୟାକେଜ୍ | | 1759-FCBGA (42.5 × 42.5) |

| ମୂଳ ଉତ୍ପାଦ ସଂଖ୍ୟା | | XC6VLX240 |

ଡକ୍ୟୁମେଣ୍ଟ୍ ଏବଂ ମିଡିଆ |

| ରିସୋର୍ସ ପ୍ରକାର | | LINK |

| ଡାଟାସିଟ୍ | Virtex-6 FPGA ଡାଟାସିଟ୍ | |

| ଉତ୍ପାଦ ତାଲିମ ମଡ୍ୟୁଲ୍ | | Virtex-6 FPGA ସମୀକ୍ଷା |

| ପରିବେଶ ସୂଚନା | Xiliinx RoHS ସାର୍ଟିଫିକେଟ୍ | |

| PCN ଡିଜାଇନ୍ / ନିର୍ଦ୍ଦିଷ୍ଟକରଣ | | କ୍ରସ୍-ସିପ୍ ଲିଡ୍-ଫ୍ରି ନୋଟିସ୍ 31 / ଅକ୍ଟୋବର / 2016 | |

ପରିବେଶ ଏବଂ ରପ୍ତାନି ବର୍ଗୀକରଣ |

| ATTRIBUTE | ବର୍ଣ୍ଣନା |

| RoHS ସ୍ଥିତି | | ROHS3 ଅନୁରୂପ | |

| ଆର୍ଦ୍ରତା ସମ୍ବେଦନଶୀଳତା ସ୍ତର (MSL) | 4 (72 ଘଣ୍ଟା) |

| REACH ସ୍ଥିତି | | REACH ଅସୁରକ୍ଷିତ | |

| ECCN | 3A001A7A |

| HTSUS | 8542.39.0001 |

XC6VLX240T-2FFG1759I FPGAs ସମୀକ୍ଷା

XC6VLX240T-2FFG1759I FPGA ଗୁଡିକ ହେଉଛି ଟାର୍ଗେଟେଡ୍ ଡିଜାଇନ୍ ପ୍ଲାଟଫର୍ମଗୁଡିକ ପାଇଁ ପ୍ରୋଗ୍ରାମେବଲ୍ ସିଲିକନ୍ ଫାଉଣ୍ଡେସନ୍ ଯାହା ଇଣ୍ଟିଗ୍ରେଟେଡ୍ ସଫ୍ଟୱେର୍ ଏବଂ ହାର୍ଡୱେର୍ ଉପାଦାନଗୁଡିକ ପ୍ରଦାନ କରିଥାଏ ଯାହା ଡିଜାଇନର୍ମାନଙ୍କୁ ସେମାନଙ୍କର ବିକାଶ ଚକ୍ର ଆରମ୍ଭ ହେବା ମାତ୍ରେ ଅଭିନବତା ଉପରେ ଧ୍ୟାନ ଦେବା ପାଇଁ ସକ୍ଷମ କରିଥାଏ |ତୃତୀୟ ପି generation ଼ିର ASMBL (ଆଡଭାନ୍ସଡ ସିଲିକନ୍ ମଡ୍ୟୁଲାର୍ ବ୍ଲକ୍) ସ୍ତମ୍ଭ-ଆଧାରିତ ସ୍ଥାପତ୍ୟ ବ୍ୟବହାର କରି, Xilinx XC6VLX240T-2FFG1759I ଅନେକ ବିଲ୍ଟିନ ସିଷ୍ଟମ ସ୍ତରୀୟ ବ୍ଲକ ଧାରଣ କରିଥାଏ |ଏହି ବ features ଶିଷ୍ଟ୍ୟଗୁଡିକ ଲଜିକ୍ ଡିଜାଇନର୍ମାନଙ୍କୁ ସେମାନଙ୍କର FPGAbased ସିଷ୍ଟମରେ ସର୍ବୋଚ୍ଚ ସ୍ତରର କାର୍ଯ୍ୟଦକ୍ଷତା ଏବଂ କାର୍ଯ୍ୟକାରିତା ନିର୍ମାଣ କରିବାକୁ ଅନୁମତି ଦିଏ |40 nm ଅତ୍ୟାଧୁନିକ ତମ୍ବା ପ୍ରକ୍ରିୟା ପ୍ରଯୁକ୍ତିବିଦ୍ୟା ଉପରେ ନିର୍ମିତ, XC6VLX240T-2FFG1759I FPGA ଗୁଡିକ କଷ୍ଟମ୍ ASIC ଟେକ୍ନୋଲୋଜି ପାଇଁ ଏକ ପ୍ରୋଗ୍ରାମେବଲ୍ ବିକଳ୍ପ |ଉଚ୍ଚ-କାର୍ଯ୍ୟଦକ୍ଷତା ଲଜିକ୍ ଡିଜାଇନର୍, ଉଚ୍ଚ-କ୍ଷମତା ସମ୍ପନ୍ନ DSP ଡିଜାଇନର୍ ଏବଂ ଉଚ୍ଚ-କାର୍ଯ୍ୟଦକ୍ଷତା ଏମ୍ବେଡ୍ ସିଷ୍ଟମ୍ ଡିଜାଇନର୍ମାନଙ୍କର ଅଦୃଶ୍ୟ ତର୍କ, DSP, ସଂଯୋଗୀକରଣ ଏବଂ କୋମଳ ମାଇକ୍ରୋପ୍ରୋସେସର୍ କ୍ଷମତା ସହିତ ଆବଶ୍ୟକ ସମାଧାନ ପାଇଁ ସର୍ବୋତ୍ତମ ସମାଧାନ ପ୍ରଦାନ କରନ୍ତୁ |

Xilinx FPGAs (ଫିଲ୍ଡ ପ୍ରୋଗ୍ରାମେବଲ୍ ଗେଟ୍ ଆରେ) ସିରିଜ୍ XC6VLX240T-2FFG1759I ହେଉଛି Virtex-6 LXT FPGA 720 I / O 1759FCBGA, ଡାଟାସିଟ୍ ସହିତ ଷ୍ଟକ୍ ଏବଂ ବିକଳ୍ପଗୁଡିକ ଦେଖନ୍ତୁ, ଷ୍ଟକ୍, FPGAkey.com ରେ ପ୍ରାଧିକୃତ ବିତରକଙ୍କ ଠାରୁ ମୂଲ୍ୟ, ଏବଂ ଆପଣ ମଧ୍ୟ ଖୋଜି ପାରିବେ | ଅନ୍ୟାନ୍ୟ FPGA ଉତ୍ପାଦଗୁଡିକ |

ବ Features ଶିଷ୍ଟ୍ୟଗୁଡିକ

ତିନୋଟି ଉପ-ପରିବାର:

Virtex-6 LXT FPGAs: ଉନ୍ନତ କ୍ରମିକ ସଂଯୋଗ ସହିତ ଉଚ୍ଚ-କାର୍ଯ୍ୟଦକ୍ଷତା ତର୍କ |

Virtex-6 SXT FPGAs: ଉନ୍ନତ କ୍ରମିକ ସଂଯୋଗ ସହିତ ସର୍ବୋଚ୍ଚ ସଙ୍କେତ ପ୍ରକ୍ରିୟାକରଣ କ୍ଷମତା |

Virtex-6 HXT FPGAs: ସର୍ବୋଚ୍ଚ ବ୍ୟାଣ୍ଡୱିଡଥ୍ କ୍ରମିକ ସଂଯୋଗ |

ଉପ-ପରିବାର ମଧ୍ୟରେ ସୁସଙ୍ଗତତା |

LXT ଏବଂ SXT ଉପକରଣଗୁଡ଼ିକ ସମାନ ପ୍ୟାକେଜରେ ପାଦଚିହ୍ନ ସୁସଙ୍ଗତ |

ଉନ୍ନତ, ଉଚ୍ଚ କ୍ଷମତା ସମ୍ପନ୍ନ FPGA ତର୍କ |

ପ୍ରକୃତ 6-ଇନପୁଟ୍ ଲୁକ୍ ଅପ୍ ଟେବୁଲ୍ (LUT) ଟେକ୍ନୋଲୋଜି |

ଡୁଆଲ୍ LUT5 (5-ଇନପୁଟ୍ LUT) ବିକଳ୍ପ |

ରିଚ୍ ରେଜିଷ୍ଟର ମିଶ୍ରଣ ଆବଶ୍ୟକ କରୁଥିବା ପ୍ରୟୋଗଗୁଡ଼ିକ ପାଇଁ LUT / ଡୁଆଲ୍ ଫ୍ଲିପ୍-ଫ୍ଲପ୍ ଯୋଡି |

ଉନ୍ନତ ମାର୍ଗଦର୍ଶନ ଦକ୍ଷତା |

64-ବିଟ୍ (କିମ୍ବା ଦୁଇଟି 32-ବିଟ୍) 6-ଇନପୁଟ୍ LUT ପ୍ରତି LUT RAM ବିକଳ୍ପ ବଣ୍ଟନ କରେ |

ପଞ୍ଜୀକୃତ ଆଉଟପୁଟ୍ ବିକଳ୍ପ ସହିତ SRL32 / ଡୁଆଲ୍ SRL16 |

ଶକ୍ତିଶାଳୀ ମିଶ୍ରିତ-ମୋଡ୍ ଘଣ୍ଟା ପରିଚାଳକ (MMCM)

MMCM ବ୍ଲକଗୁଡିକ ଶୂନ-ବିଳମ୍ବ ବଫରିଂ, ଫ୍ରିକ୍ୱେନ୍ସି ସିନ୍ଥେସିସ୍, ଘଣ୍ଟା-ପର୍ଯ୍ୟାୟ ସ୍ଥାନାନ୍ତର, ଇନପୁଟ୍ଜିଟର ଫିଲ୍ଟରିଂ ଏବଂ ଫେଜ୍-ମେଳକ ଘଣ୍ଟା ବିଭାଜନ ପ୍ରଦାନ କରିଥାଏ |

36-Kb ବ୍ଲକ RAM / FIFOs |

ଉଚ୍ଚ କ୍ଷମତା ସମ୍ପନ୍ନ ସମାନ୍ତରାଳ SelectIO ଟେକ୍ନୋଲୋଜି |

ଉନ୍ନତ DSP48E1 ସ୍ଲାଇସ୍ |

ନମନୀୟ ବିନ୍ୟାସ ବିକଳ୍ପଗୁଡ଼ିକ |

SPI ଏବଂ ସମାନ୍ତରାଳ ଫ୍ଲାସ୍ ଇଣ୍ଟରଫେସ୍ |

ଉତ୍ସର୍ଗୀକୃତ ଫଲବ୍ୟାକ୍ ପୁନ f ବିନ୍ୟାସ ତର୍କ ସହିତ ମଲ୍ଟି-ବିଟ୍ଷ୍ଟ୍ରିମ୍ ସମର୍ଥନ |

ସ୍ୱୟଂଚାଳିତ ବସ୍ ଓସାର ଚିହ୍ନଟ |

ସମସ୍ତ ଡିଭାଇସରେ ସିଷ୍ଟମ୍ ମନିଟର କ୍ଷମତା |

ଅନ୍-ଚିପ୍ / ଅଫ୍-ଚିପ୍ ଥର୍ମାଲ୍ ଏବଂ ଯୋଗାଣ ଭୋଲଟେଜ୍ ମନିଟରିଂ |

ସମସ୍ତ ମନିଟରିଂ ପରିମାଣକୁ JTAG ପ୍ରବେଶ |

PCI ଏକ୍ସପ୍ରେସ ଡିଜାଇନ୍ ପାଇଁ ଇଣ୍ଟିଗ୍ରେଟେଡ୍ ଇଣ୍ଟରଫେସ୍ ବ୍ଲକ୍ |

GTX ଟ୍ରାନ୍ସସିଭର: 6.6 Gb / s ପର୍ଯ୍ୟନ୍ତ |

FPGA ତର୍କରେ ଓଭରସମ୍ପଲିଂ ଦ୍ୱାରା 480 Mb / s ତଳେ ଡାଟା ହାର ସମର୍ଥିତ |

GTH ଟ୍ରାନ୍ସସିଭର: 2.488 Gb / s ରୁ 11 Gb / s ରୁ ଅଧିକ |

ଇଣ୍ଟିଗ୍ରେଟେଡ୍ 10/100/1000 Mb / s ଇଥରନେଟ୍ MAC ବ୍ଲକ |

GTX ଟ୍ରାନ୍ସସିଭର ବ୍ୟବହାର କରି 1000BASE-X PCS / PMA ଏବଂ SGMII କୁ ସମର୍ଥନ କରେ |

SelectIO ଟେକ୍ନୋଲୋଜି ଉତ୍ସ ବ୍ୟବହାର କରି MII, GMII, ଏବଂ RGMII କୁ ସମର୍ଥନ କରେ |

2500Mb / s ସମର୍ଥନ ଉପଲବ୍ଧ |

40 nm ତମ୍ବା CMOS ପ୍ରକ୍ରିୟା ପ୍ରଯୁକ୍ତିବିଦ୍ୟା |

1.0V କୋର୍ ଭୋଲଟେଜ୍ (-1, -2, -3 ସ୍ପିଡ୍ ଗ୍ରେଡ୍)

ଲୋ-ପାୱାର୍ 0.9 ଭି କୋର୍ ଭୋଲଟେଜ୍ ବିକଳ୍ପ (-1L ସ୍ପିଡ୍ ଗ୍ରେଡ୍)

ଷ୍ଟାଣ୍ଡାର୍ଡ କିମ୍ବା Pb- ମୁକ୍ତ ପ୍ୟାକେଜ୍ ବିକଳ୍ପଗୁଡ଼ିକରେ ଉଚ୍ଚ ସଙ୍କେତ-ଅଖଣ୍ଡତା ଫ୍ଲିପ୍-ଚିପ୍ ପ୍ୟାକେଜିଂ ଉପଲବ୍ଧ |